【Zynq7】1.FSBL(1stStageBootLoader)の構築

1.記事一覧

記事は複数回に分けて投稿します。Zynq7020SoCで動作する、YoctoベースのPetaLinuxを使わない素のLinuxを構築します。

エッジArm Linux構築編(armv7l)

- 【Zynq7】Yoctoを使わずに素のLinuxをソースから構築する

- 【Zynq7】1.FSBL(1stStageBootLoader)の構築 ←本ページ

- 【Zynq7】2.U-bootの構築

- 【Zynq7】3.Linuxカーネルの構築

- 【Zynq7】4.Zyboz7ボードのデバイスツリー構築

- 【Zynq7】5.RootFSのマウント(Ubuntu18.04)

- 【Zynq7】6.カーネルモジュールの配置

- 【Zynq7】番外編1.u-bootが途中で止まる問題

- 【Zynq7】番外編2.MACアドレスをQSPIFlashから読み出して設定する

エッジArm Linux実践編(armv7l)

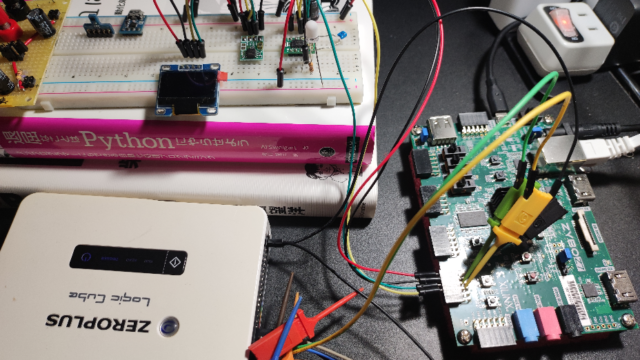

- 【Zynq7】実践1. LinuxにRTCを認識させる【I2Cデバイス】

- 【Zynq7】実践2. 温度センサをPython+Dockerで使う【I2Cデバイス】

- 【Zynq7】実践3. 組込みLinuxでコンテナ導入に苦労した話【Docker Engine編】

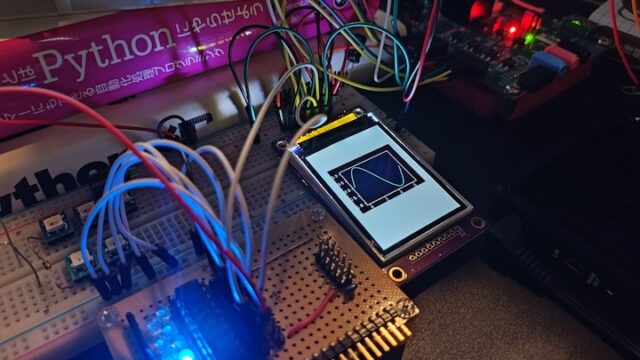

- 【Zynq7】実践4. LinuxでSPIを使う【液晶編1】

- 【Zynq7】実践5. ZynqPLのGPIOをLinuxで使う【液晶編2】

- 【Zynq7】実践6. PythonでSPI液晶を使う【液晶編3】

- 【Zynq7】閑話. SPI バス周波数が上がらない問題

2.環境

参考書の内容より新しいVivadoとVitisのバージョンを使用します。これらは先にインストール済みの前提で進めます。開発PCにUbuntuを使用していますが、Windowsでも問題ありませんが、U-boot以降の手順はLinux環境が必要になるので、WSL2を使用するなどしてください。

| 開発PC | Ubuntu20.04, intel core i5 750 RAM 16G |

| Xilinxツール | Vivado,Vitis 2022.2(現在最新2023/1) |

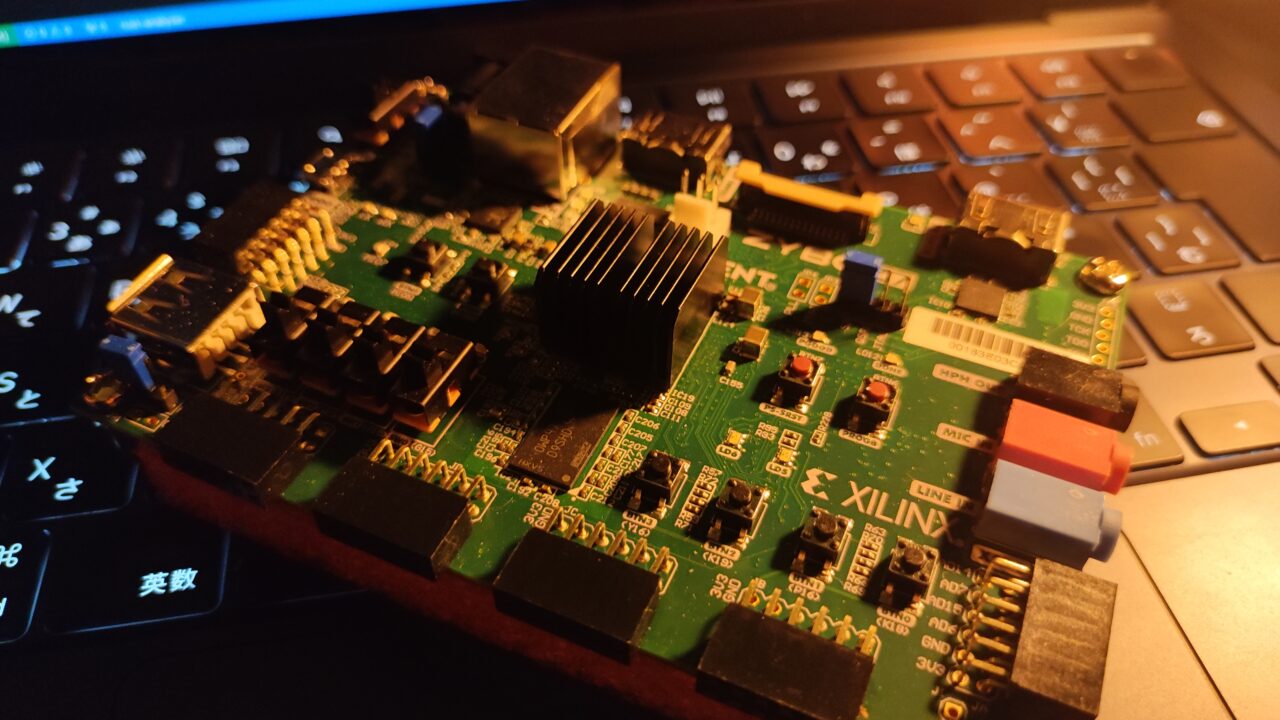

| ターゲットボード | Digilent Zybo z7-20 Rev.B.2 (XC7Z020-1CLG400C, DDR3 1GB) |

3.FSBL作成の流れ

FSBL作成の流れを説明します。FSBL(First Stage Boot loader)はハードウェアの初期化を行い、U-bootブートローダを呼び出すための前段のブートローダになります。

今回はZynqSoCデバイスにかなり依存する内容のため、Zynqデバイスの概要や作法を説明します。まず、ZynqSoCについて簡単に説明します。

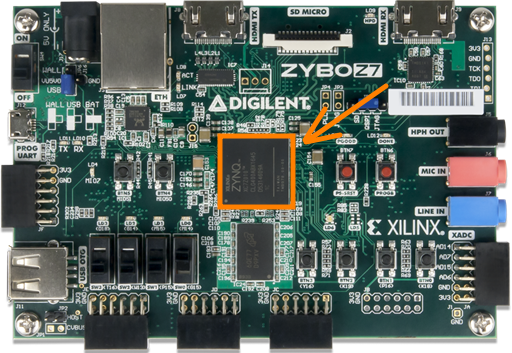

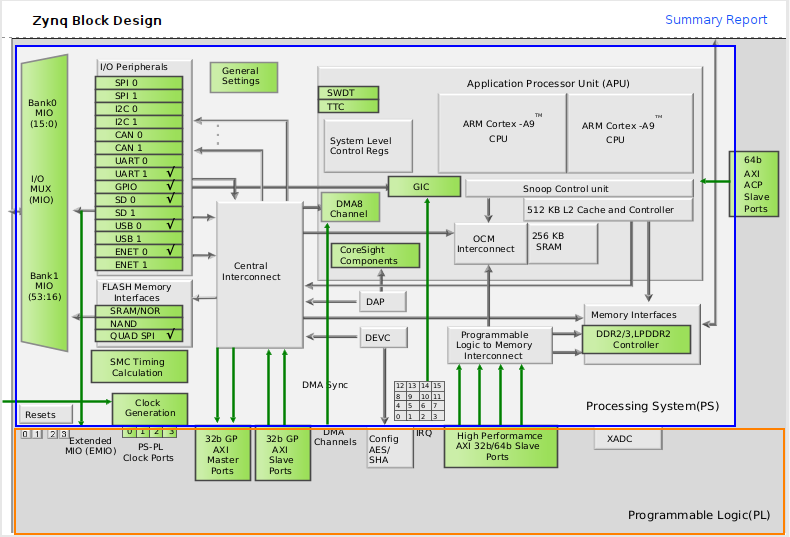

出典<https://japan.xilinx.com/products/boards-and-kits/1-t5lnks.html>

ZynqデバイスはXilinx(ザイリンクス、現在はAMD傘下)社製のARMプロセッサを搭載するFPGA SoCです。橙色枠のPL部(ProgrammableLogic)と青枠のPS部(ProcessingSystem)に別れています。PL部はFPGAに該当します。PS部はArmプロセッサ(Cortex-A9×2)とDDRメモリコントローラ、クロック、そしてI/Oペリフェラルで構成されます。

Xilinxツールの開発の流れです。FSBLとBitStreamの2つのファイルを作る必要があります。

- Vivadoにより、PS部のIPを配置し、バス、クロック信号を配線する

- Vivadoでハードウェアを構成するための情報BitStreamファイルを生成する

- Vivadoからハードウェア情報をVitisに移動し、BSP(BoardSupportPackage)を生成

- VitisはPSのプロセッサで実行するFSBLプログラムをビルドし生成する

ポイントは

- Vivado(ハードウェア(BitStream)構築)→Vitis(ソフトウェア(FSBL)構築)の流れ

4.VivadoによるPL部の設定とBitStream生成

Vivado(読み:ビバド)はFPGA開発向けのツールになります。プロジェクトを作成し、ハードウェア構成情報のBitStreamデータを生成していきます。

4-1. プロジェクト作成

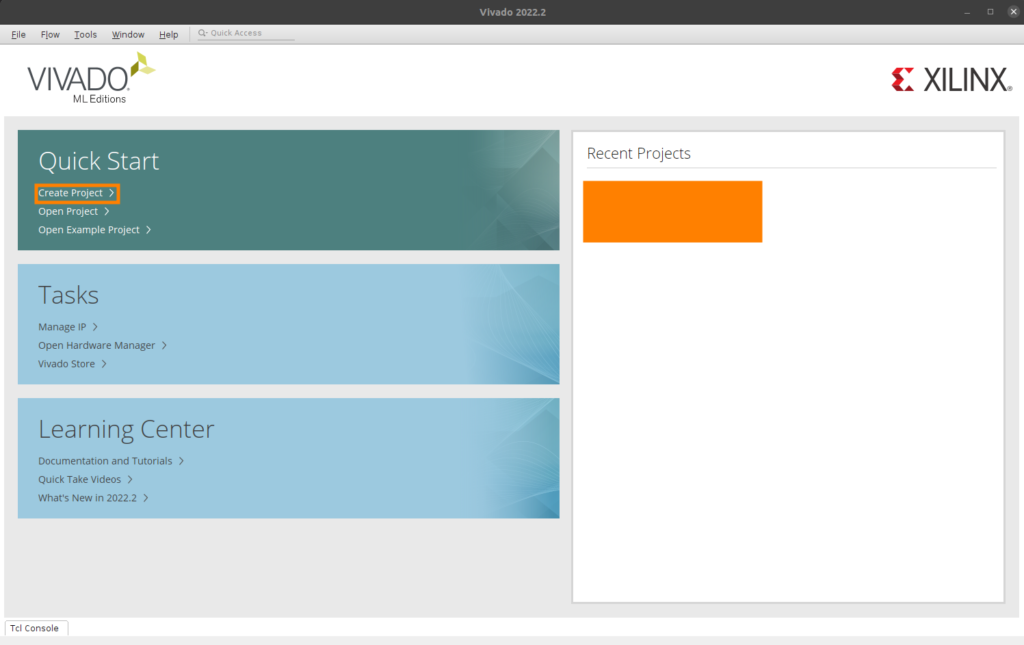

Vivadoを立ち上げ、Quick Start>Create Projectで新規作成します。

$ source /tools/Xilinx/Vivado/2022.2/settings64.sh

$ source /tools/Xilinx/Vitis/2022.2/settings64.sh

$ vivado &

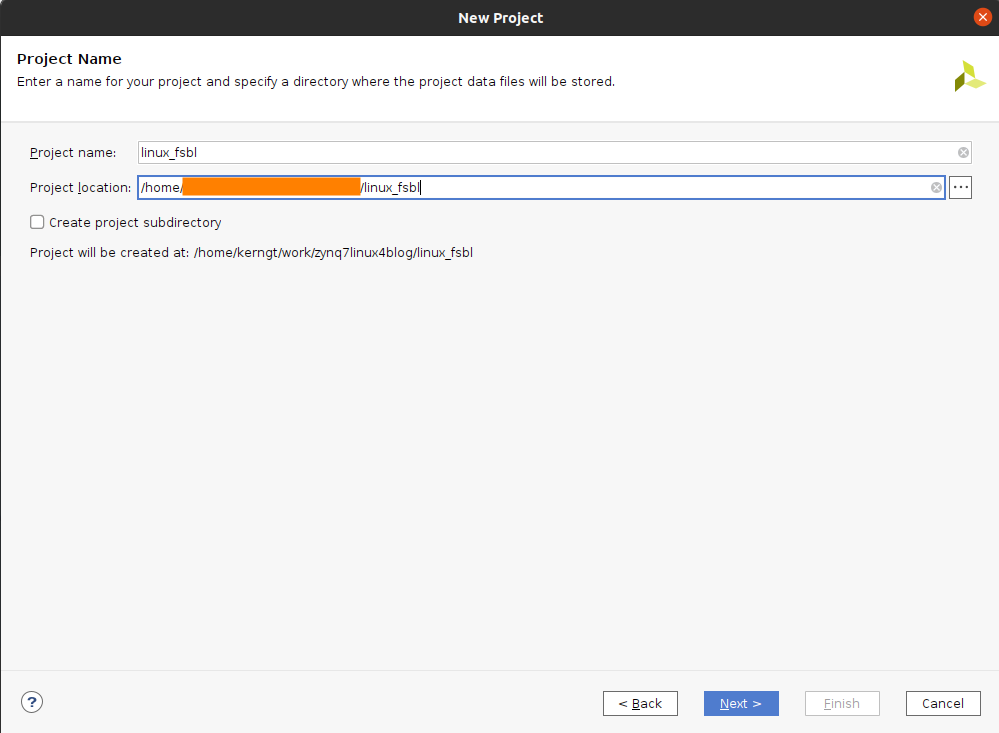

nextをクリックしプロジェクト名を入力し、フォルダを選択します。

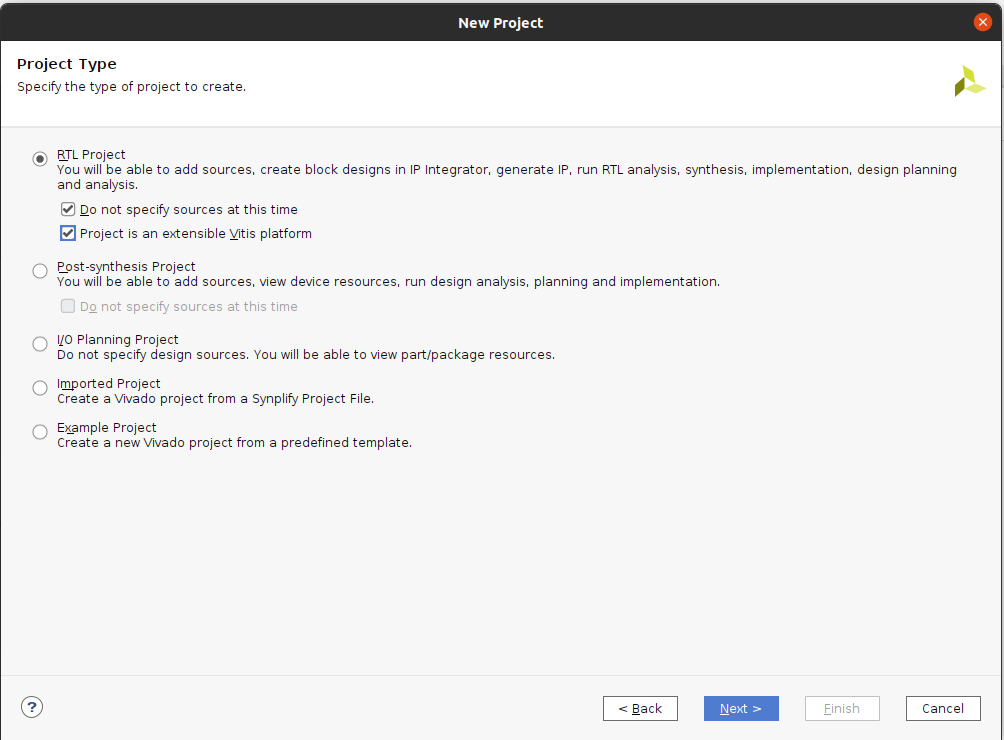

RTL Projectと2つのチェックを入れnextします。

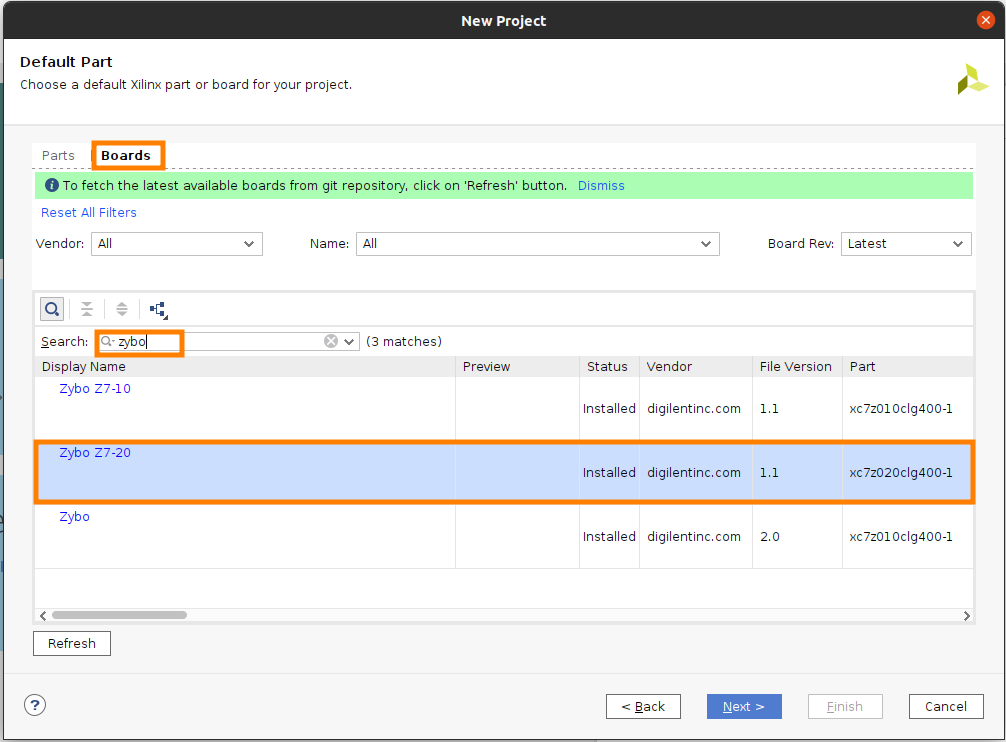

Boardsタブを選択し、Searchに”zybo”と入力、今回のターゲットボードである、「Zybo Z7-20」を選択し、nextします。

次のページでFinishをクリックすると、プロジェクト生成完了です。

4-2. PS部にクロックを供給する

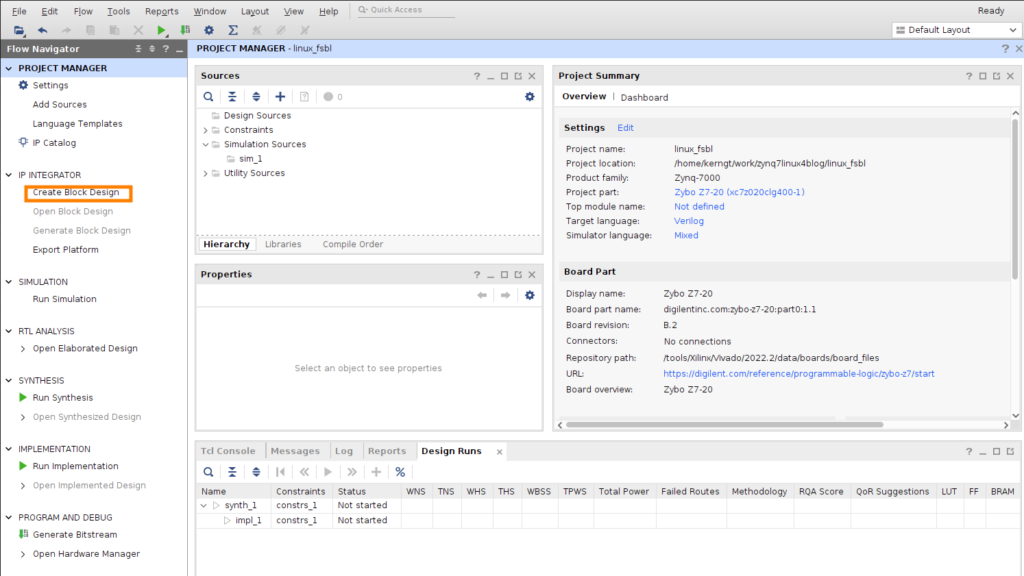

クロックの設定をしていきます。IPコンフィグレータを使用し、IPをブロック線図のように配置、配線を行います。IP(Intellectual Property)とは誤解を恐れず言うと回路情報でここではハードウェアのブロックとして扱います。左カラムの「Create Block Design」をクリックします。

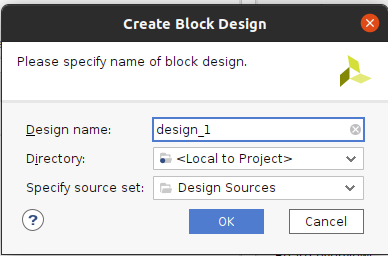

デフォルトでOKをクリックします。

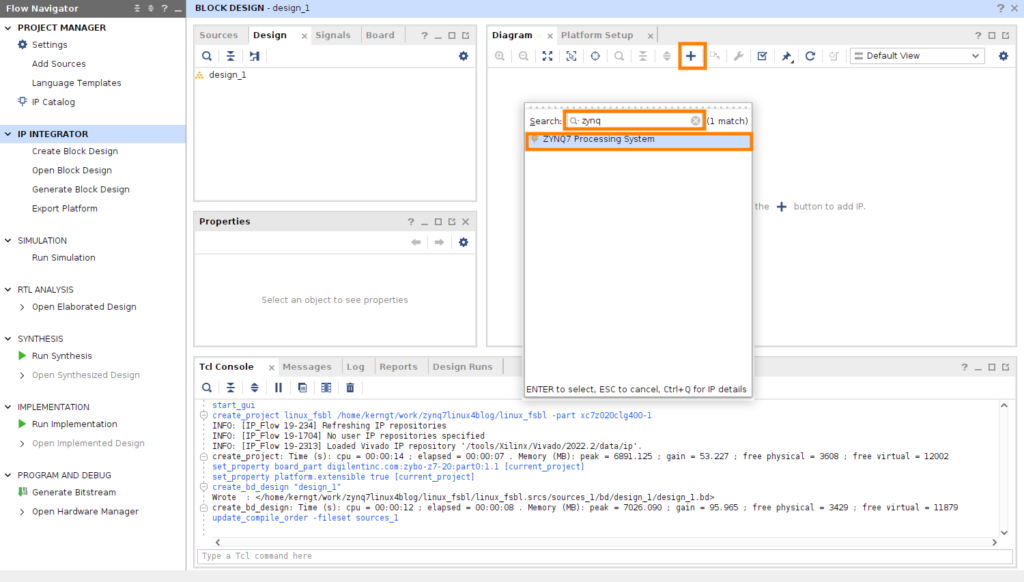

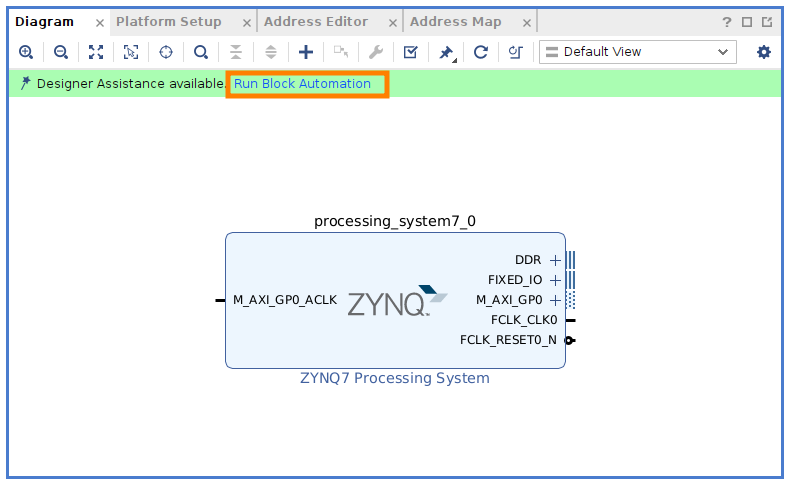

「+」印のAddIPをクリックし、表示されたリストに「zynq」と入力、ZYNQ7 Processing Systemをダブルクリックすると、IPブロックが追加されます。

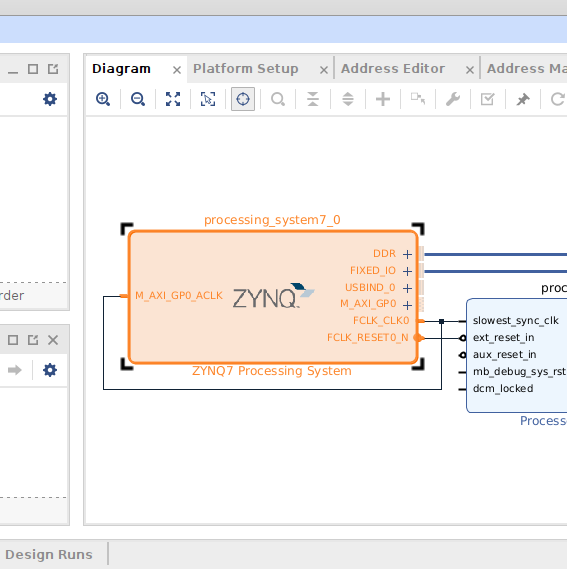

PS部のIPブロックが配置されました。Run Block Automationをクリックし、自動配線します。

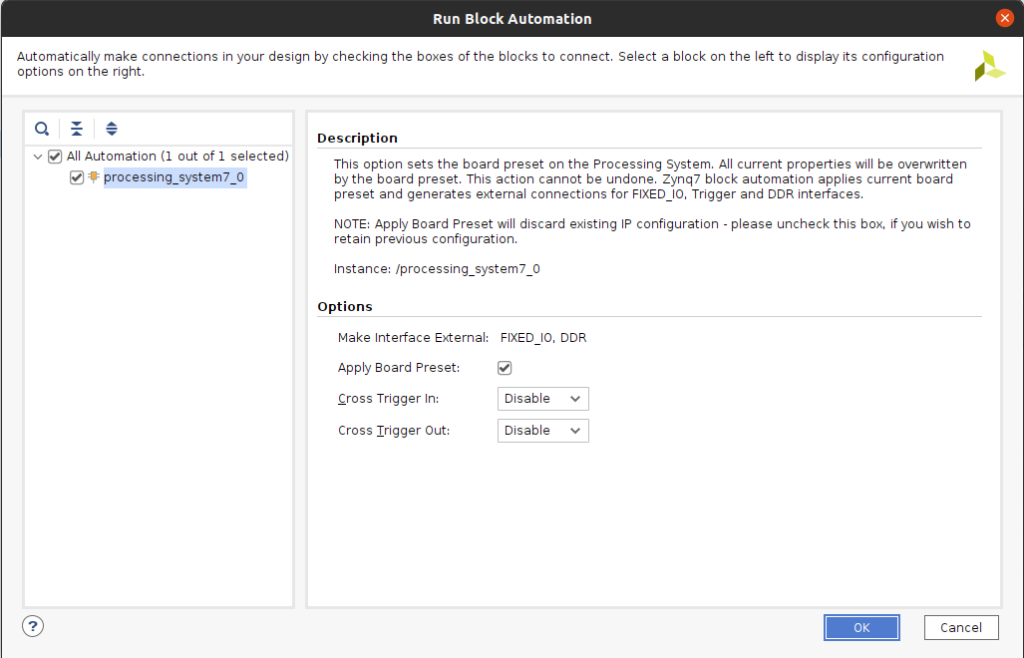

デフォルトでOKをクリックします。

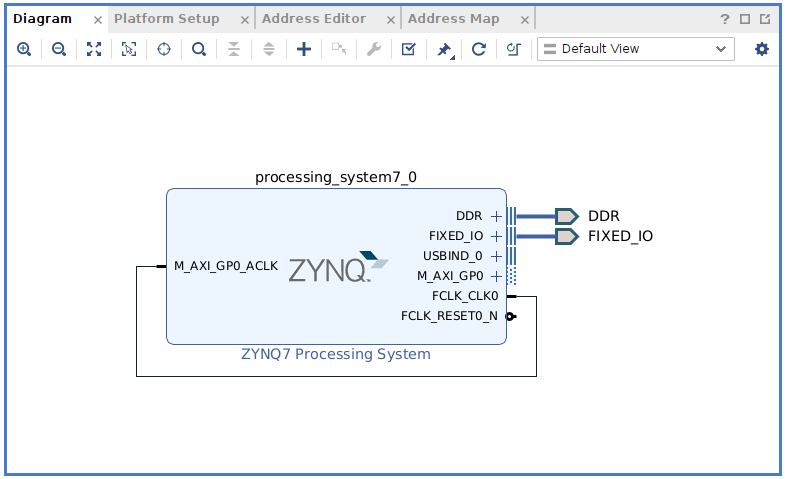

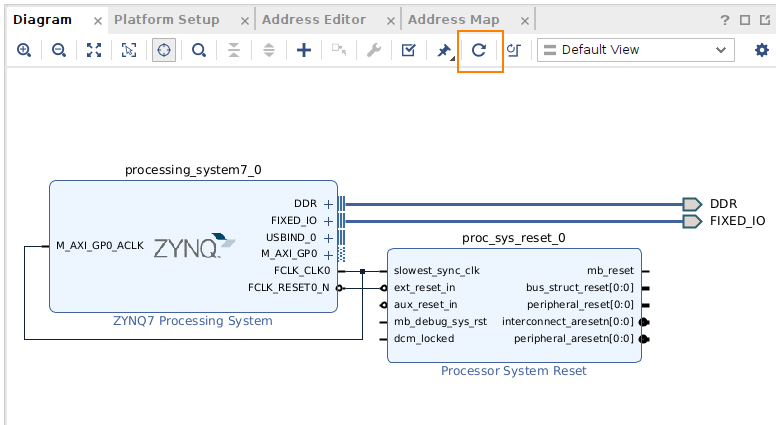

DDR SDRAMインターフェイスとFIXED_IOが自動配線されます。次にクロックを手動で配線します。FCLK_CLK0をドラッグしながらM_AXI_GP0_ACLKに接続してください。

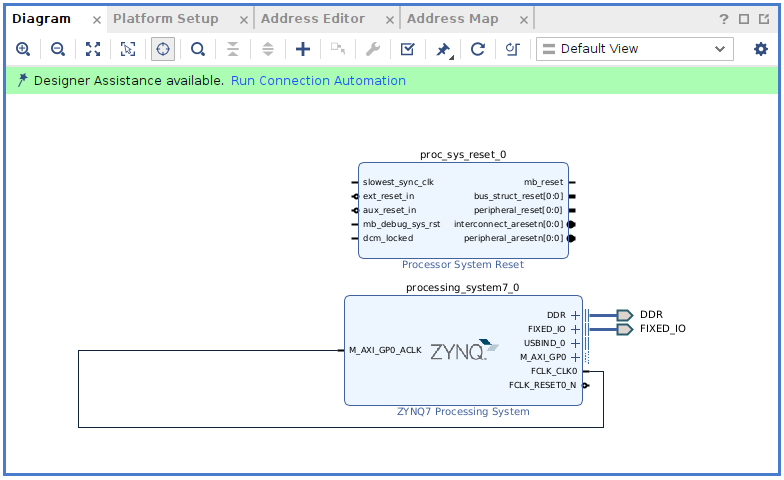

次にリセット生成IPを配置します。「+」印のAddIPをクリックし、表示されたリストに「reset」と入力、Processor System Resetをダブルクリックすると、IPブロックが追加されます。

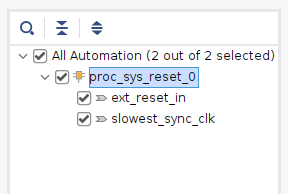

Run Block Automationをクリックし、自動配線します。ウィンドウが出てきたらすべてチェックを入れてください。

配線が完了するので、Regenerate Layoutボタンをクリックして、配置を整理します。

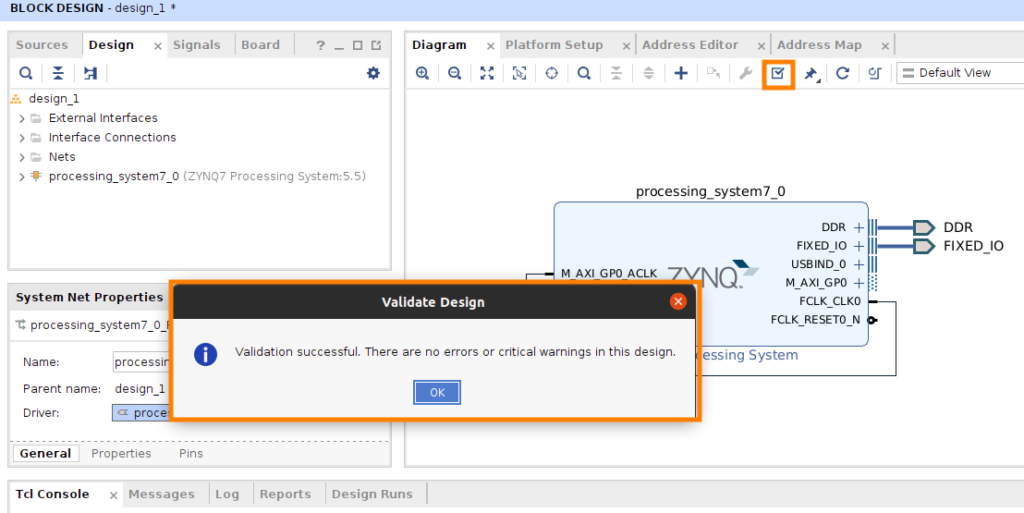

配線のチェックを行います。Validate Designボタンをクリックします。

エラーがでなければ問題ありません。しかし、DDR周りで警告が出る場合は無視して良いです(PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY_x)。DDRの信号タイミング設定値がマイナス値であるため警告が出ていますが、zyboボード固有の設定値になるので、変える必要はありません。

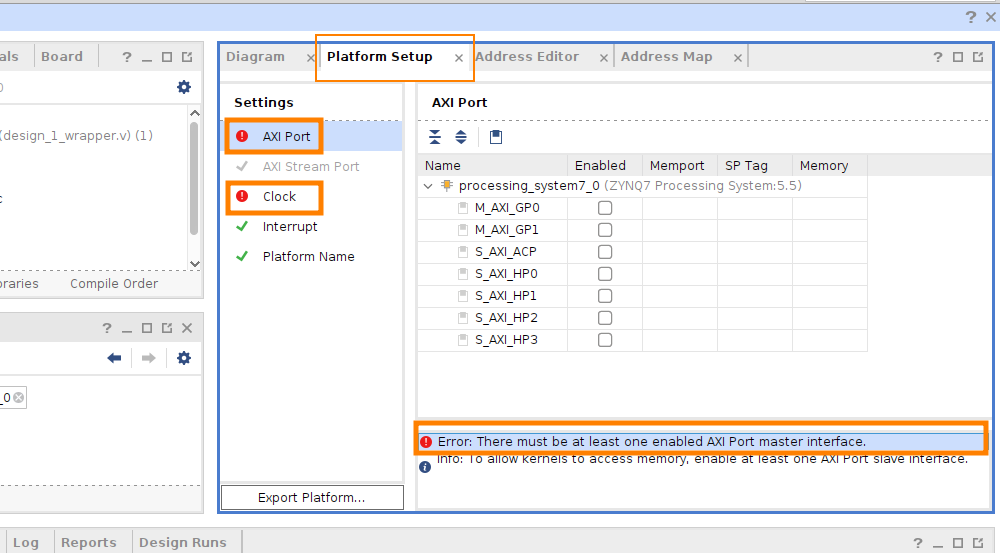

次にPlatform Setupタブを選択して、エラーがあれば解消します。エラーを残すと、この後、Vitis向けにハードウェア情報をExportできなくなります。

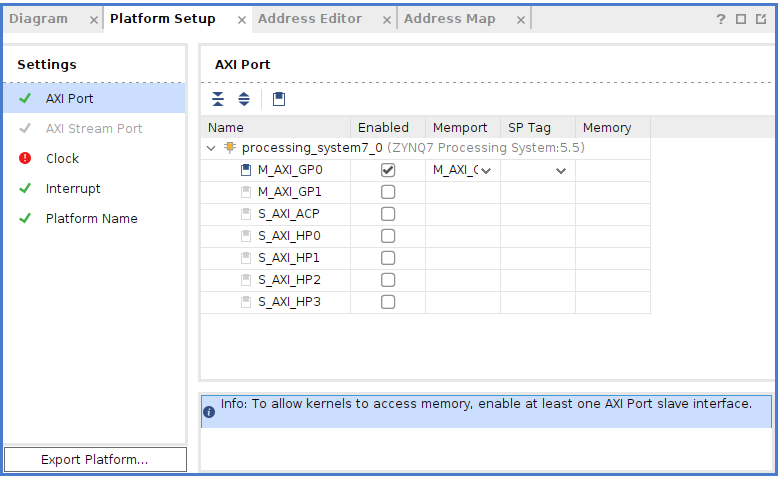

AXI Portの設定をします。AXI Portバスマスタを最低1つ有効にしろとエラー書きがあるので、M_AXI_GP0のEnabledをチェックします。AXIPortとはPS-PL間のバスの接続部分を指します。今回はPL側にバススレーブIPを何も配置していないので使いません。

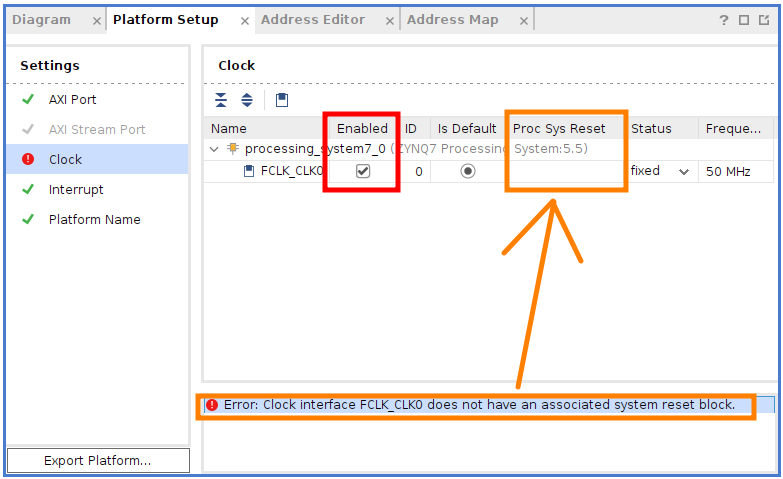

つづいてClockです。FCLK_CLK0に関連するリセットブロックが無いよと注意書きがあります。リセットブロックは先ほど追加したリセット生成IPのことです。再認識させるために、Enabledのチェックを一度外し、入れ直します。

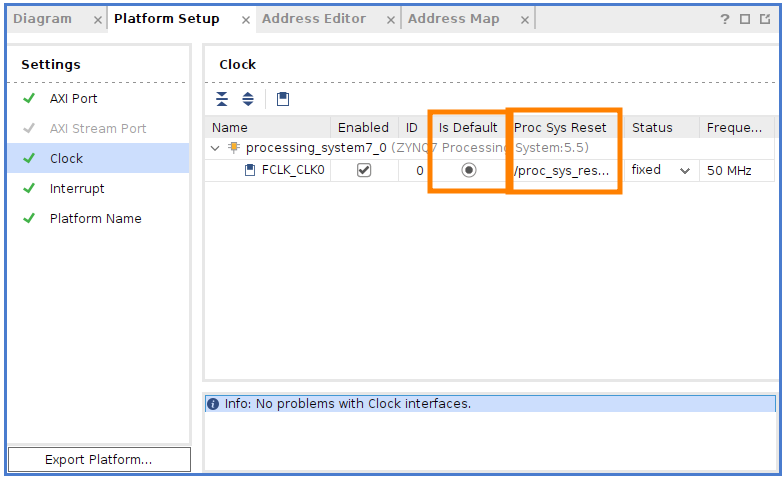

Is Defaultのチェックも入れ直します。リセット生成IPが認識されてエラーが消えます。

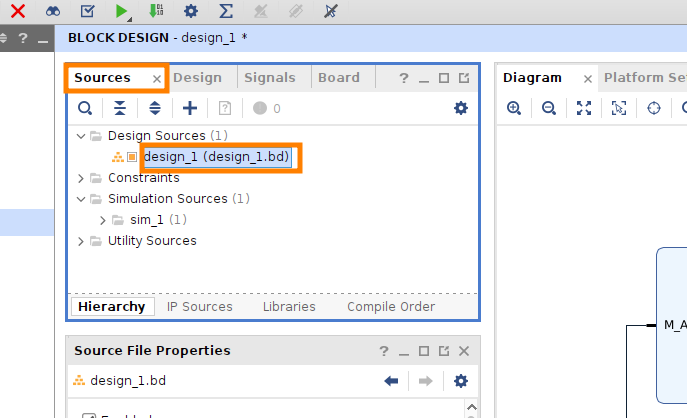

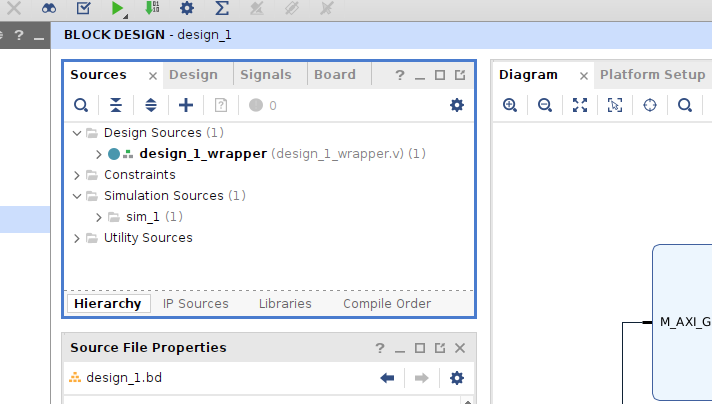

続いてプロジェクトの上位階層を作成します。BitStreamを生成するために必要な階層になります。Sourcesウィンドウ>Design Sources>design_1(design_1bd)を右クリックし、Create HDL Wrapperをクリックします(右クリックメニューのスクショ写っていませんがご了承ください)。

オプションのダイアログはそのままOKをクリックしてください。完了すると”*_wrapper”に変わります。

4-3. 制約ファイルの読み込みと論理合成・配置配線の実行

制約ファイルを読み込みます。制約ファイルとはFPGAやZynqデバイスの端子に関しての

- 回路記述のポートに対するFPGA外部端子の割当

- 各端子の信号レベルを設定

- クロック周波数の波形の設定

を記述したファイル(.xdc)になります。zyboボードのメーカーであるDigilentより配布されていますので、これを利用します。コメントアウトされているので各々で外して使います。

私が改変したZybo-Z7-Custom.xdcをおいておきます。これをvivadoのプロジェクトフォルダ内にコピーします。

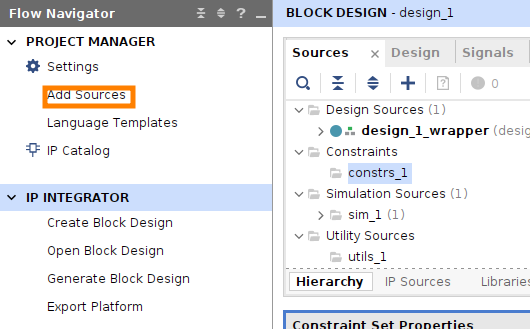

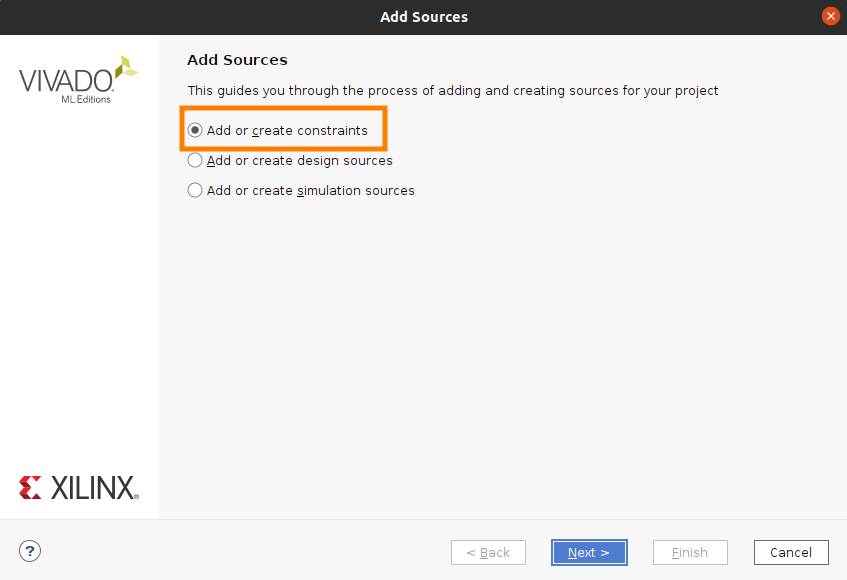

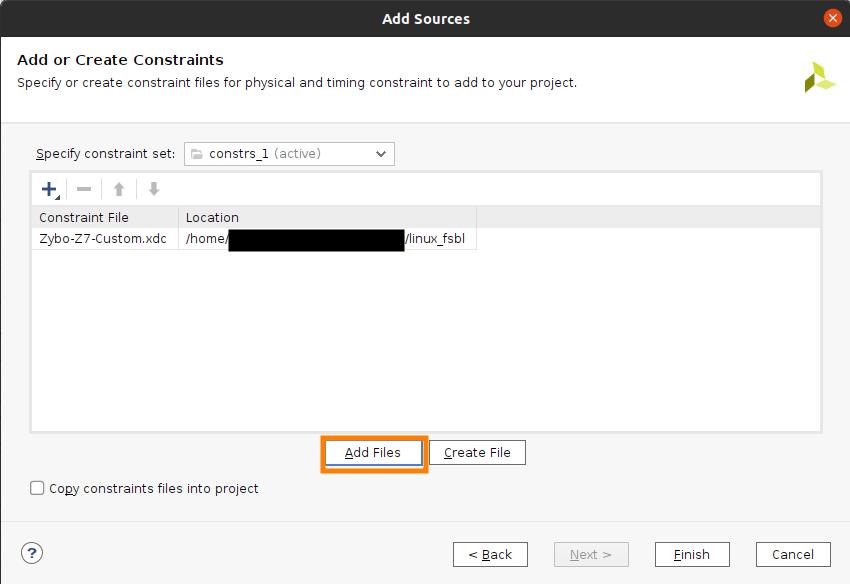

Add Sourcesをクリックし、Add or create constraintsを選択してnextをクリックします。

Add Filesを押して先ほどプロジェクト内にコピーした.xdcファイルを取り込みます。

Finishを押して完了です。

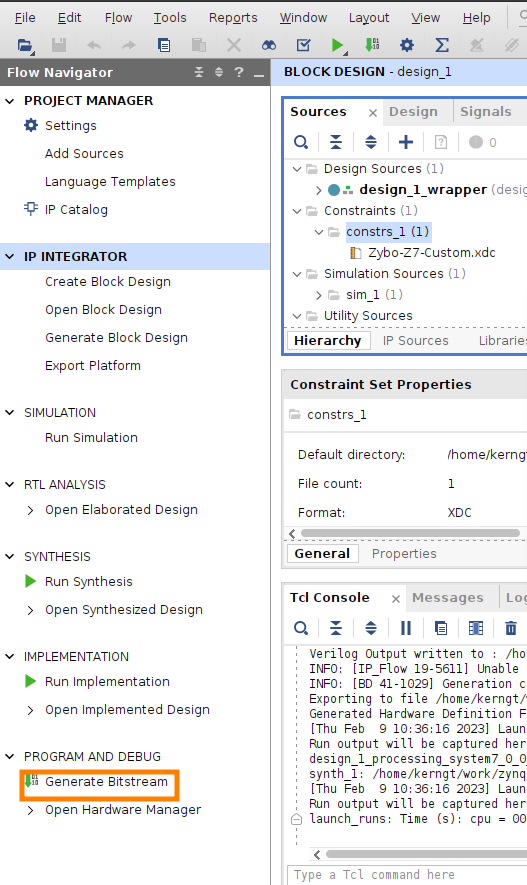

最後に論理合成・配置配線を行い、BitStreamファイルを出力します。論理合成・配置配線は詳細な説明は省きますが、ソフトウェアで言うコンパイル工程のようなものです。左下のPROGRAM AND DEBUG>Generate Bitstreamをクリックします。

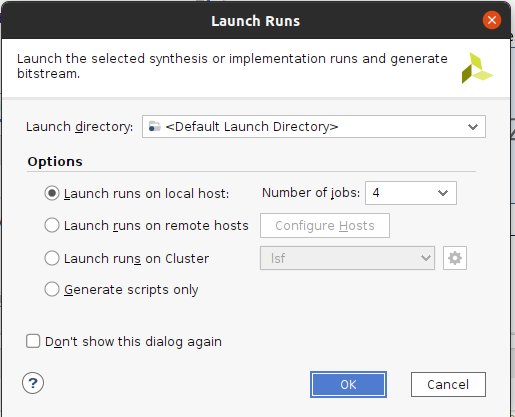

実行ジョブ数のダイアログが出ますが、そのままOKします。

「No Implementation Results Available」のメッセージが出たらYesをクリックします。

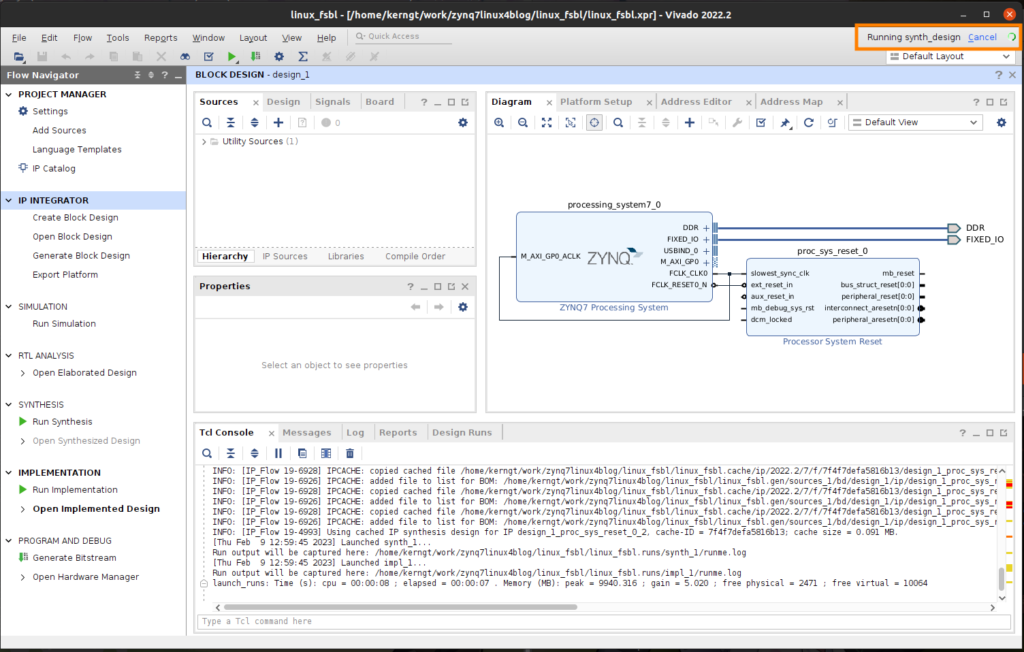

論理合成・配置配線が開始します。開発PCのスペックによりますが、5~10分かかります。ウィンドウ右上の緑のぐるぐるマークがチェックになるまで待ちます。

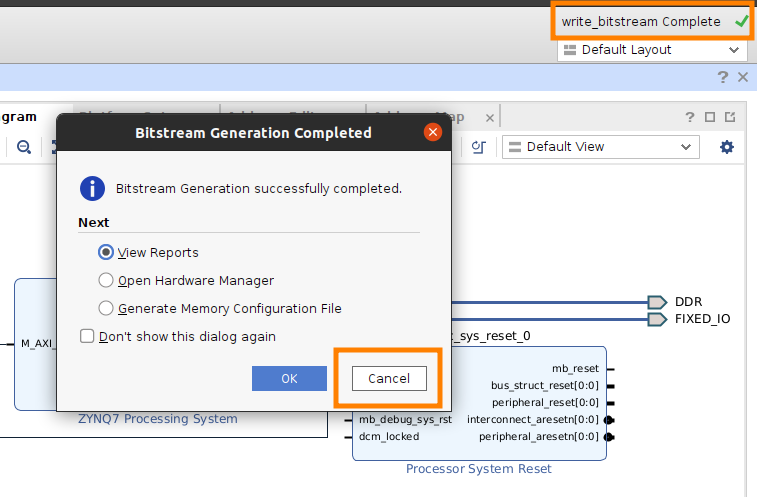

終了すると、Bitstream Generation successfully completed.とメッセージが出れば問題ありません。キャンセルして閉じます。

BitstreamファイルはVivadoプロジェクトフォルダ内の

“プロジェクト名.runs/impl_1/design_1_wrapper.bit”

にあります。

5.VitisによるFSBLの生成

Vitis(読み:バイティス)はZynq搭載のARMプロセッサのソフトウェアを開発するツールです。これでFSBLソースコードをビルドしていきます。

5-1. Vivadoからハードウェア情報をエクスポート

VitisでFSBLを生成するために、先ほど作成したVivadoのハードウェア情報を読み込む必要があります。まずはVivadoよりプラットフォームファイルをエクスポートします。

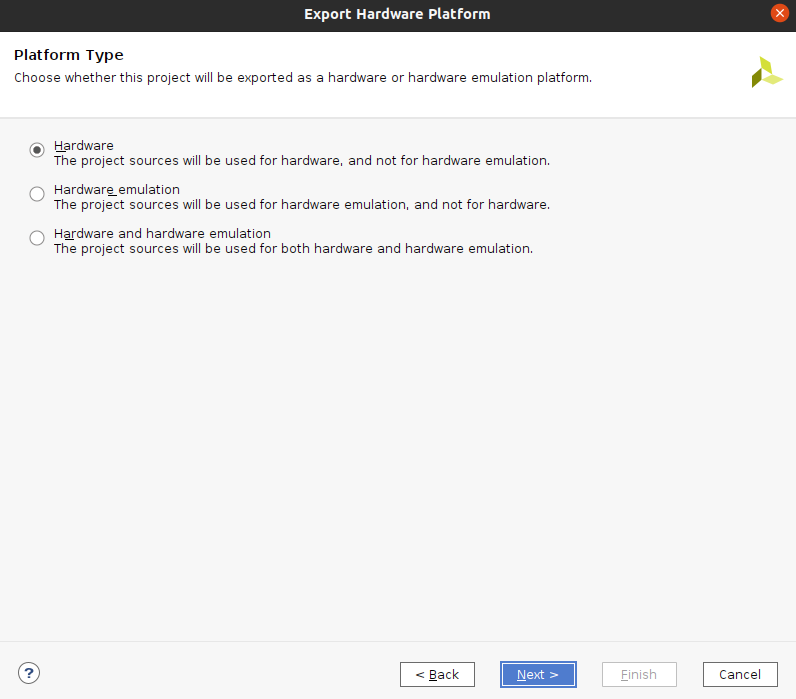

Vivadoの左上File>Export>Export Platform…をクリックします。ウィンドウが出てくるのでNextをクリック。Platform TypeはHardwareを選択します。

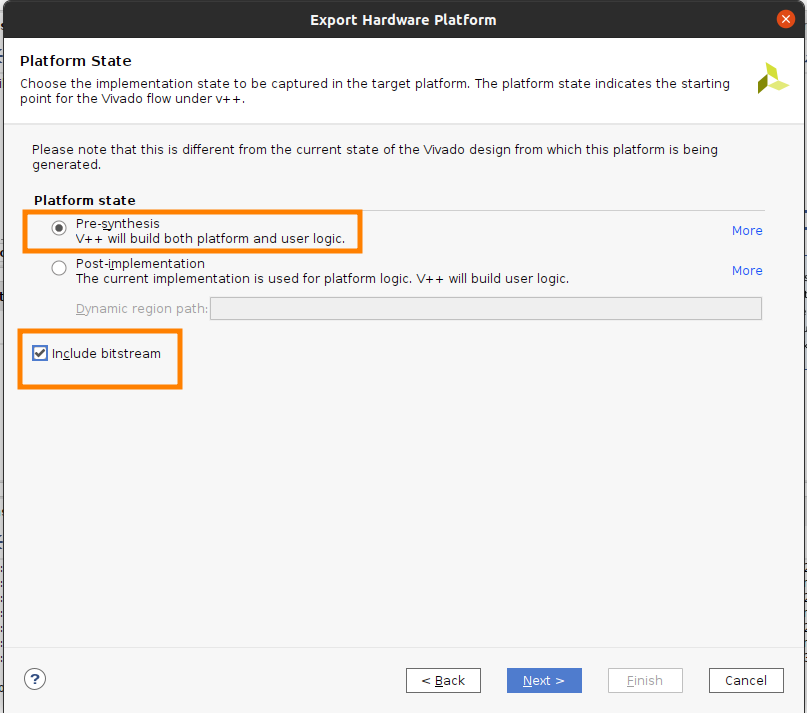

Pre-synthesisを選択し、Include bitstreamをチェックしてnextをクリックします。

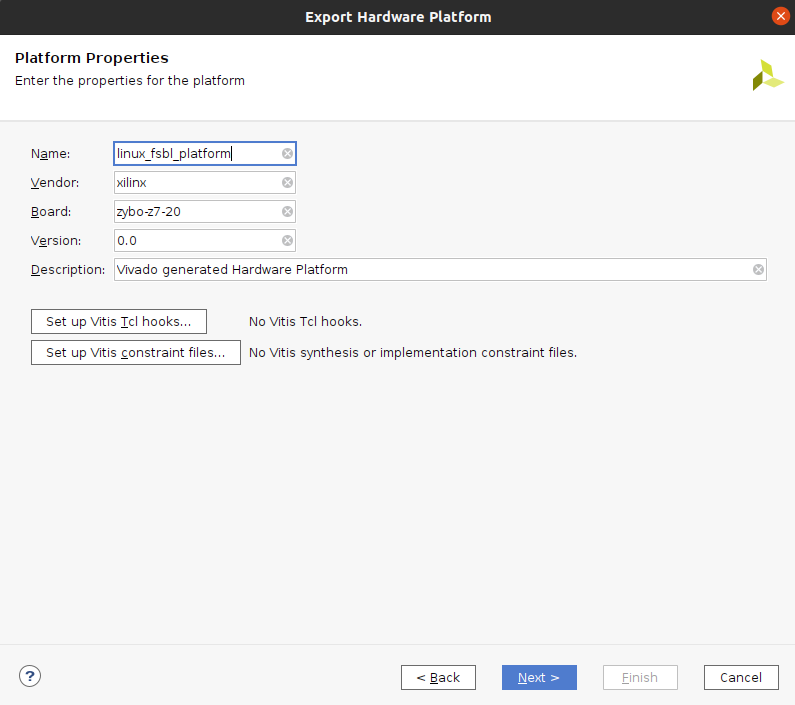

platform名を入力してnextをクリック。

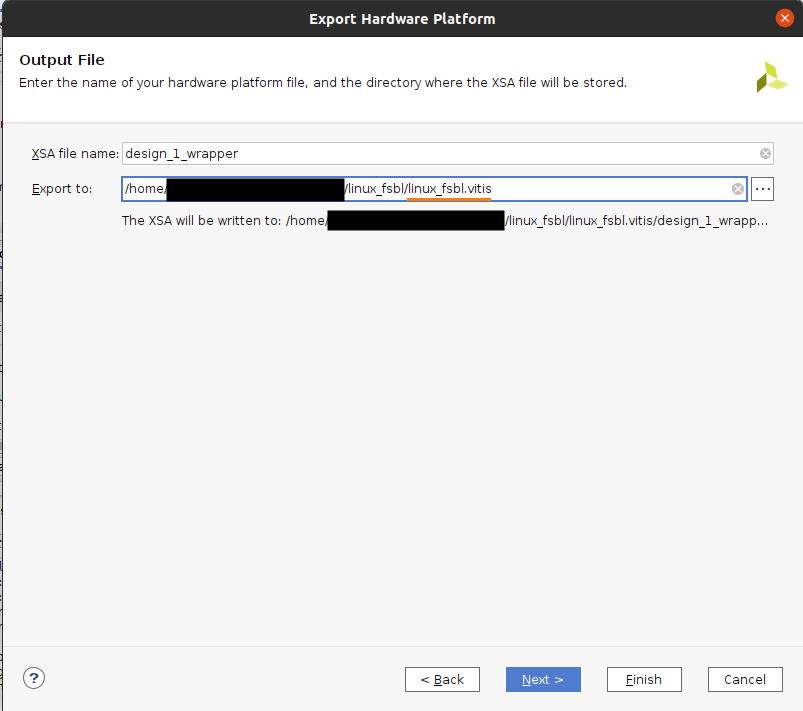

保存先を指定します。デフォルトのパスのままだとVitisで大量のファイルが生成されてVivadoのファイルと混ざって大変なことになるため、Vivadoプロジェクト内に「プロジェクト名.vitis」サブフォルダを作成してその中に保存することにします。

最後にfinishをクリックして完了です。.xsaファイルが生成されます。

5-2. Vitisのプロジェクトの作成

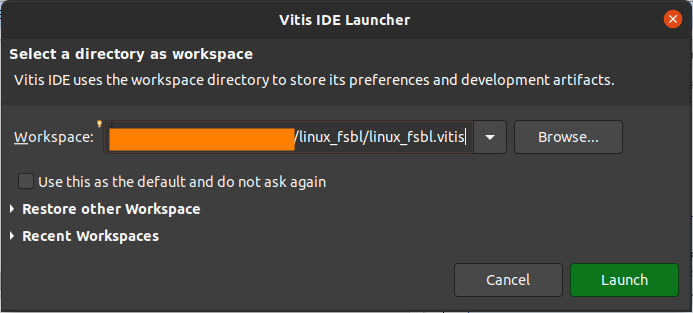

Vivadoの左上ToolsからLaunch Vitis IDEをクリックして起動します。workspaceはvivadoでエクスポートしたプロジェクト名.vitisフォルダにします。

【追記】アプリケーションプロジェクトの作成は不要でした。プラットフォームプロジェクト作成時の”Generate boot components”にチェックが入っていればLinuxがブートできるFSBLが作成されます。逆にアプリケーションプロジェクトを作成すると、FSBLが2重に生成されて、VivadoでHWの更新が反映されません。申し訳ございません。

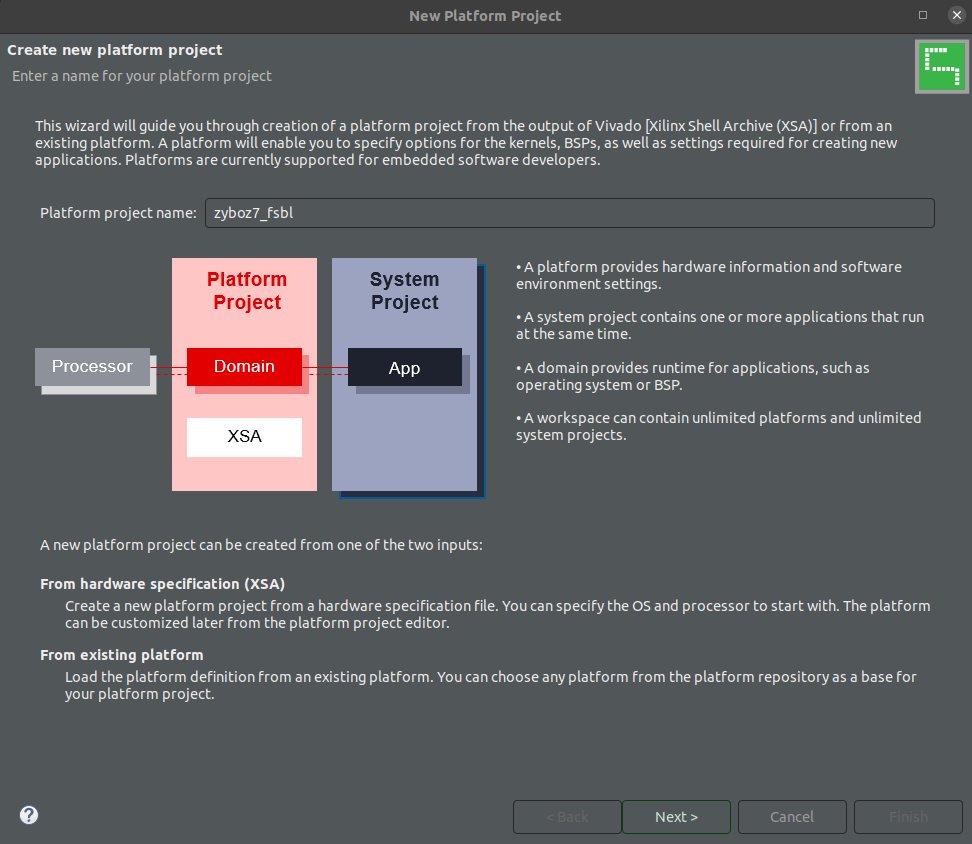

【修正版】Create new platform projectでプラットフォームプロジェクトを作成します。プロジェクト名は適当です。

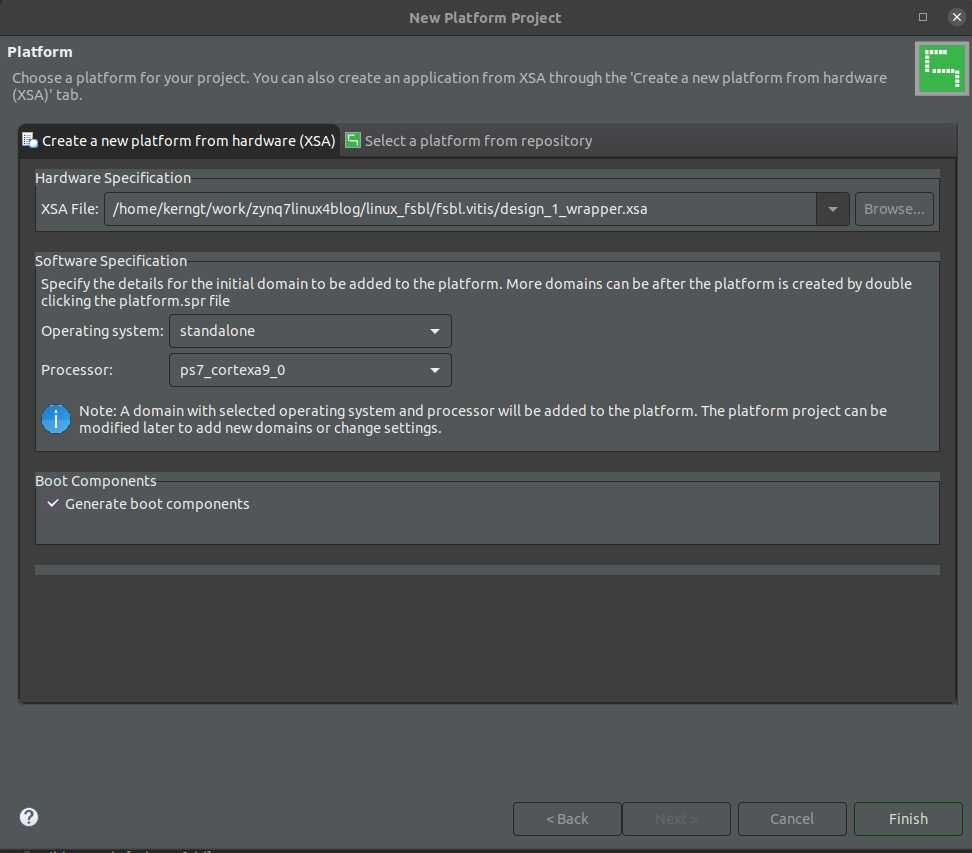

先程Vivadoからexportしたプラットフォームファイル(.xsa)を選択します。以下を選択します。

- Operating System : standalone

- Processor : ps7_cortex9_0

- Generate boot components -> チェックを入れる

finishを押して完了です。

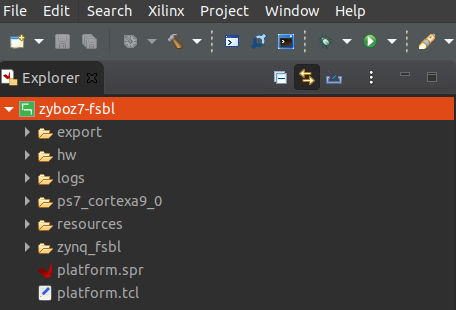

5-3. FSBLをビルドする

左のプラットフォームプロジェクト(zyboz7-fsbl)を選択し金槌アイコンを押してビルドします。ソースコードフォルダ内に”fsbl.elf”が生成されたら完了です。

この.elfファイルがFSBLになります。場所は以下にあります。

“ワークスペース名.vitis/プラットフォームプロジェクト名/zynq_fsbl/fsbl.elf”

以上で必要なBitStreamファイルとFSBLが用意できました。

6.(参考)FSBLの設定

6-1. シリアルデバッグメッセージの有効化

なひたふさんの本には、FSBLの設定のポイントがいくつか乗っています。今回はシリアルコンソールにデバッグメッセージを表示する例を参考に設定してみます。

Zyboz7ボードにはオンボードデバッガが搭載されています。デバッガの回路図は非公開ですが、基板上のチップはFTDIのFT2232HQです。1本のUSBケーブルを接続すると、JTAGと仮想COMポートを使用することができます。

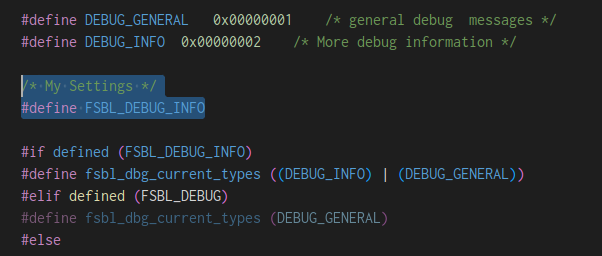

Vitisプロジェクトのsrc/fsbl_debug.hを適当なエディタで開き、

“#if defined (FSBL_DEBUG_INFO)”

のコンパイルスイッチ手前にFSBL_DEBUG_INFOマクロを定義します。下図のように記載します。

6-2. UARTポートの選択

Zynq z7ボードに搭載されるZynq7020SoCはUART0、UART1の2つあります。

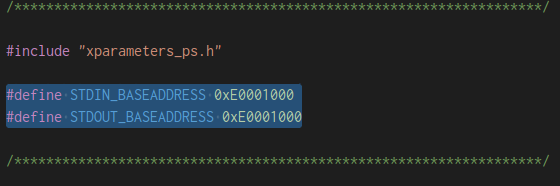

USBJTAGケーブルではUART1が接続されていますが、コンソール出力がきちんと選択されているか確認します。確認する場所はplatformフォルダのbspのコードです。以下のパスにあります。

”workspase/design_1_wrapper_1(plarform名)/ps7_cortexa9_0/standalone_ps7_cortexa9_0/bsp/ps7_cortexa9_0/include/xparameters.h”

UART0=0xE0000000、UART1= 0xE0001000のアドレスになりますので設定は問題ありません。UART0を使いたい場合はこちらを切り替えます。

6-3. UART通信速度の設定

LInuxを起動する場合、実行権がFSBL→U-boot→Linuxと移ります。UARTの通信速度はそれぞれで設定し直されるので注意してください。どれかが異なるとLinux起動中にメッセージの文字化けや文字が出なくなったりします。私はU-boot(115.2kbps)からLinux起動直後に9600bpsに切り替わって、メッセージが出ず、起動失敗したと勘違いしたことがありました。

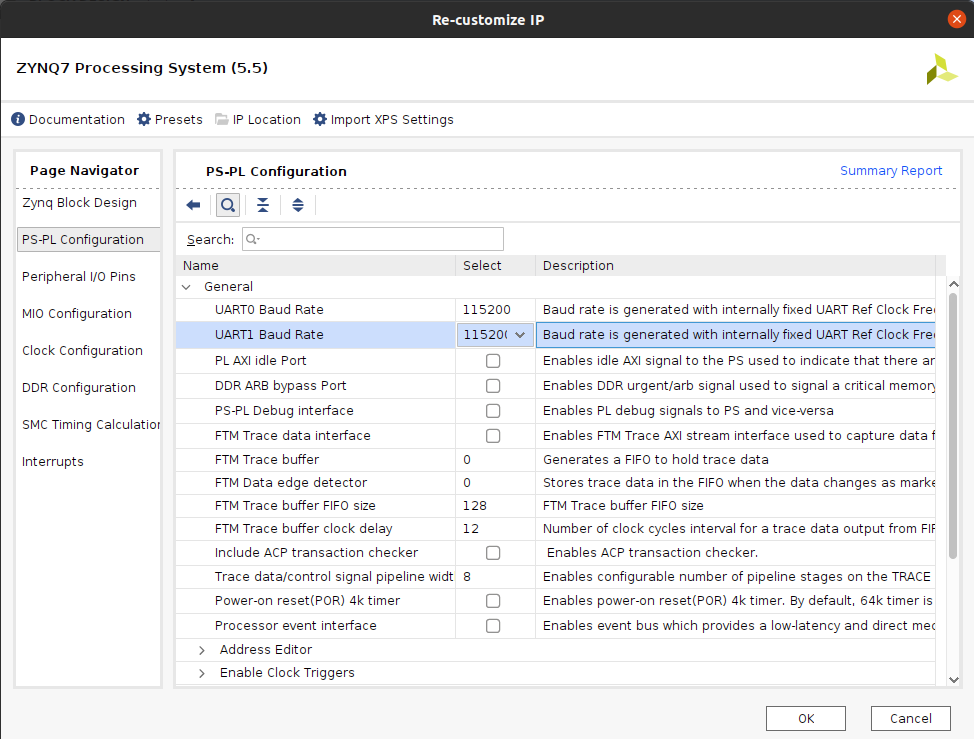

さて、FSBL実行中の通信設定です。vivadoのIPコンフィグレータでPS部のIPを配置したと思います。そのIPをダブルクリックします。

PS-PL Configration > General > UART1 Baud Rateで設定できます。

設定を変更したら、bitstreamの生成し直し、プラットフォーム情報のエクスポート、VitisでFSBLの再ビルドが必要になります。